© 2021 Carl Pearson

#### MOVEMENT AND PLACEMENT OF NON-CONTIGUOUS DATA IN DISTRIBUTED GPU COMPUTING

BY

CARL PEARSON

#### DISSERTATION

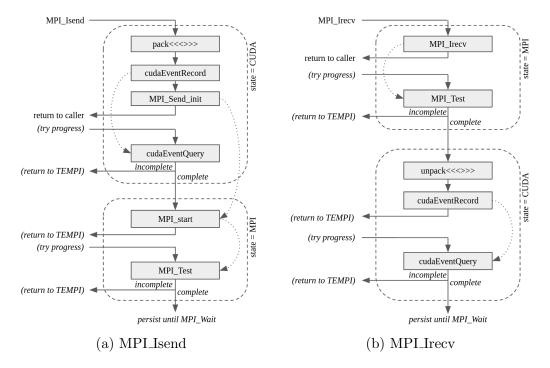

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois Urbana-Champaign, 2021

Urbana, Illinois

Doctoral Committee:

Professor Wen-Mei Hwu, Chair Associate Professor Steven Lumetta Professor Luke Olson Professor Sanjay Patel Adjunct Research Professor Jinjun Xiong

## Abstract

Steady increase in accelerator performance has driven demand for faster interconnects to avert the memory bandwidth wall. This has resulted in wide adoption of heterogeneous systems with varying underlying interconnects, and has delegated the task of understanding and copying data to the system or application developer. Data transfer performance on these systems is now impacted by many factors including data transfer modality, system interconnect hardware details, CPU caching state, CPU power management state, driver policies, virtual memory paging efficiency, and data placement.

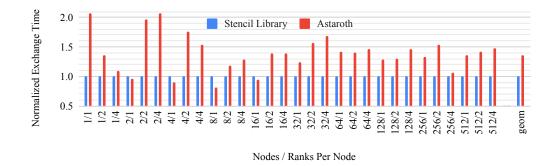

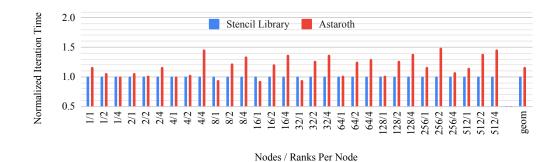

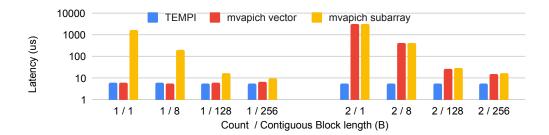

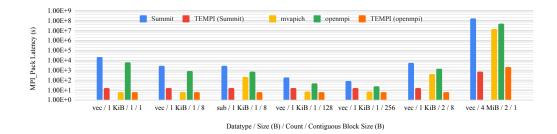

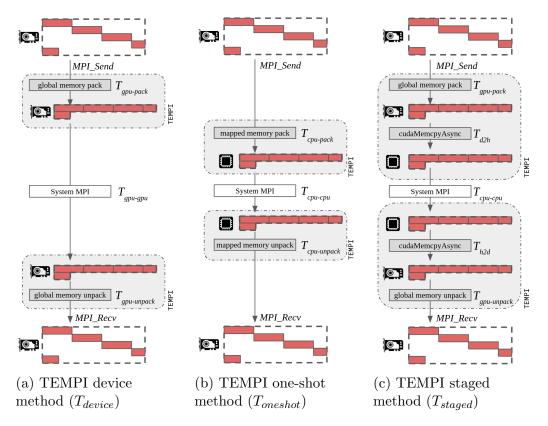

This work finds that empirical communication measurements can be used to automatically schedule and execute intra- and inter-node communication in a modern heterogeneous system, providing "hand-tuned" performance without the need for complex or error-prone communication development at the application level. Empirical measurements are provided by a set of microbenchmarks designed for system and application developers to understand memory transfer behavior across different data placement and exchange scenarios. These benchmarks are the first comprehensive evaluation of all GPU communication primitives. For communication-heavy applications, optimally using communication capabilities is challenging and essential for performance. Two different approaches are examined. The first is a high-level 3D stencil communication library, which can automatically create a static communication plan based on the stencil and system parameters. This library is able to reduce iteration time of a state-of-the-art stencil code by  $1.45 \times$  at 3072 GPUs and 512 nodes. The second is a more general MPI interposer library, with novel non-contiguous data handling and runtime implementation selection for MPI communication primitives. A portable pure-MPI halo exchange is brought to within half the speed of the stencil-specific library, supported by a five order-of-magnitude improvement in MPI communication latency for non-contiguous data.

To my wife, for her support, guidance, and cool head.

# Acknowledgments

I would like to thank my committee for their valuable feedback and guidance. This work is supported by IBM-ILLINOIS Center for Cognitive Computing Systems Research (C3SR) - a research collaboration as part of the IBM AI Horizon Network. This research used resources of the Oak Ridge Leadership Computing Facility at the Oak Ridge National Laboratory, which is supported by the Office of Science of the U.S. Department of Energy Contract No. DE-AC05-00OR22725. This work utilizes resources supported by the National Science Foundation's Major Research Instrumentation program, grant #1725729, as well as the University of Illinois at Urbana-Champaign. I would also like to thank Dawei Mu, Omer Anjum, I-Hsin Chung, and Mert Hidayetoglu.

# Table of Contents

| Chapter 1 Intro                                       | duction $\ldots$ | 1 |  |  |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------|---|--|--|

| Chapter 2 Back                                        | ground                                                                                            | 4 |  |  |

| 2.1 CUDA S                                            | ystem                                                                                             | 4 |  |  |

| 2.2 CUDA R                                            | Runtime API vs. CUDA Operation                                                                    | 4 |  |  |

| 2.3 CUDA S                                            | treams and Events                                                                                 | 5 |  |  |

| 2.4 Data Mo                                           | ovement in CUDA Systems                                                                           | 6 |  |  |

| 2.5 Synchror                                          | nous and Asynchronous CUDA Operations                                                             | 7 |  |  |

| 2.6 MPI                                               |                                                                                                   | 8 |  |  |

| Chapter 3 Meas                                        | surements                                                                                         | 9 |  |  |

| 3.1  Comm Second                                      | cope Design                                                                                       | 9 |  |  |

| 3.2 Libscope                                          | m Design                                                                                          | 3 |  |  |

| 3.3 Observat                                          | tions and Guidelines                                                                              | 6 |  |  |

| 3.4 Conclusio                                         | on                                                                                                | 4 |  |  |

| Chapter 4 3D S                                        | tencil Halo Exchange Library                                                                      | 8 |  |  |

| 4.1 Distribut                                         | ted Stencil Overview                                                                              | 9 |  |  |

| 4.2 Challeng                                          | es with CUDA+MPI Stencil Codes                                                                    | 2 |  |  |

|                                                       | titioning $\ldots$ $\ldots$ $\ldots$ $\ldots$ $3$                                                 | 4 |  |  |

| 4.4 Subgrid                                           | Placement                                                                                         | 6 |  |  |

| 4.5 Specializ                                         | ation $\ldots \ldots 3$     | 7 |  |  |

|                                                       |                                                                                                   | 4 |  |  |

| 4.7 Conclusion                                        | on                                                                                                | 8 |  |  |

| Chapter 5 Non-contiguous Data Optimization for MPI 61 |                                                                                                   |   |  |  |

| 5.1 Astaroth                                          | Communication in MPI 6                                                                            | 3 |  |  |

| 5.2 MPI Stri                                          | ided Datatype Handling 6                                                                          | 8 |  |  |

|                                                       | $pe\_commit$                                                                                      | 2 |  |  |

|                                                       | k and MPI_Unpack                                                                                  | 3 |  |  |

|                                                       | d, MPLRecv, and Performance Modeling 8                                                            | 5 |  |  |

|                                                       | d/Irecv                                                                                           | 1 |  |  |

|                                                       | artitioning for Data Placement                                                                    | 3 |  |  |

| -                                                     | er Library                                                                                        | 5 |  |  |

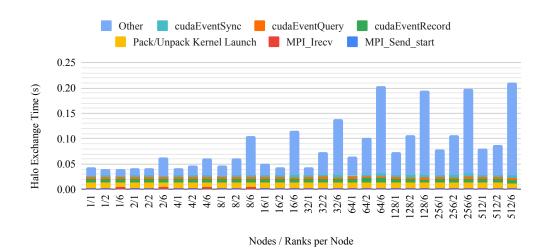

| -                                                     | cil Evaluation                                                                                    | 0 |  |  |

| 5.10 Conclusion $\ldots \ldots \ldots$ |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 6 Related Work                                                                                                                                 |

| 6.1 CUDA Communication Benchmarks                                                                                                                      |

| 6.2 3D Stencil                                                                                                                                         |

| 6.3 MPI Datatype Handling                                                                                                                              |

| 6.4 Scientific Libraries                                                                                                                               |

| Chapter 7 Conclusion and Future Work                                                                                                                   |

| 7.1 Conclusion $\ldots \ldots \ldots$  |

| 7.2 Future Work $\ldots \ldots 114$                  |

| Appendix Artifacts                                                                                                                                     |

| References                                                                                                                                             |

## Chapter 1

## Introduction

With the end of Dennard scaling, computer architects have sought to satisfy demand for increasing performance by providing specialized hardware accelerators tuned to computation with particular characteristics. Perhaps the most successful example of this trend is the widespread adoption of graphics processing units (GPUs) for more general data-parallel compute tasks. With the success of GPUs as a template, architects are moving forward with a wide variety of accelerators, such as SIMD extensions [1, 2, 3], AI accelerators (Google tensor processing unit [4], Huawei Neural Processing Unit [5], IBM neuromorphic chips [6], Intel Nervana [7]), motion coprocessors (Apple M-series [8]), field-programmable gate arrays (Xilinx Virtex [9], Intel Stratix [10]), network processors (Netronome Agilio [11]), digital signal processors (Qualcomm Hexagon [12], NXP DSP56xx Family [13]), vision processing units (Eyeriss [14], Movidius VPU [15], Mobileye EyeQ [16], Microsoft Holographic Processing Unit [17]) and many others. These heterogeneous systems have become the dominant system architecture.

The enormous compute capability accelerators demands high-bandwidth data access to "feed the beast." Without this bandwidth, the performance potential of the accelerator is largely wasted waiting for data. The trend of integration (also motivated by reduction of total system cost) where semiconductor die-size or power limits allow has provided one approach to solving this problem. By integrating an accelerator onto the same die as the CPU, the accelerator more easily gets high-bandwidth low-power access to data shared with the CPU. For accelerators with high memory demands, however, the system memory DRAM bandwidth may ultimately limit performance.

The second approach is to provide accelerators with their own high-performance memory. Unfortunately, managing this memory then falls upon runtime systems or the application developer, and moving data into accelerator memory to support high-performance execution is a first-order design consideration for any accelerated application. The data-placement and datamovement challenge is exacerbated by the growing demand for data-driven applications. Analytics and neural-network applications ingest huge amounts of data, and even if the computation per data element is small, the aggregate computation can be commensurately large. That motivates developers to use accelerators for these applications. To achieve high performance on accelerators, developers must marshal and coordinate their data movement and computation in heterogeneous systems.

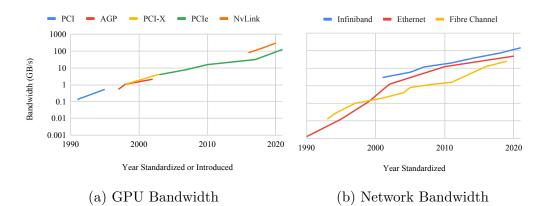

Figure 1.1: Growth of interconnect bandwidth over time. In all cases, the fastest configuration is used (e.g., 16 lanes of PCIe 3.0).

For accelerators with their own limited high-performance memory, the effect of the interconnect on the overall system performance has not escaped notice. Figure 1.1 shows the rapid growth of GPU interconnect bandwidth over time, by year introduced (NVLink) or standardized (PCI, AGP, PCI-X, PCIe) [18, 19, 20, 21, 22, 23, 24, 25, 26, 27, 28]. As the importance of these interconnects grows, they also are used as the backbone for various software-and hardware-backed coherency schemes between accelerators and host components. Performance of the interconnects that tie accelerators together is the foundational motivation for this work.

This work finds that empirical communication measurements can be used to automatically schedule and execute intra- and inter-node communication in a modern heterogeneous system, providing "hand-tuned" performance without the need for complex or error-prone communication development at the application level. This is demonstrated through the development and evaluation of a high-level communication library for distributed stencil codes. Since the communication library automatically discovers and applies relevant techniques, substantial performance improvement is realized for an existing application, which was limited by implementation complexity and lack of optimization for the evaluation platform. The primary downside of implementing the techniques in a high-level library is that existing applications would need to be modified to use it. To that end, this work also demonstrates how a widely-used communication interface can use the same empirical measurements.

The rest of this document is organized as follows:

- Chapter 2 describes background information on heterogeneous computers and the CUDA programming system, Linux NUMA system, and MPI.

- Chapter 3 describes the design, implementation, and evaluation of the CUDA communication microbenchmarks. These microbenchmarks are the first comprehensive measurement of point-to-point bulk CUDA communication methods, and provide the empirical measurements.

- Chapter 4 describes and evaluates how insights from the benchmarks can be used to automatically plan and execute communication without system knowledge from the application developer. The evaluation is conducted by developing, deploying, and analyzing a high-level stencil library and includes analysis of techniques that influence performance in different circumstances.

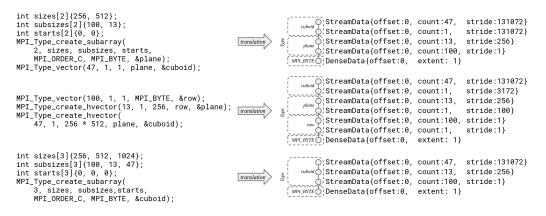

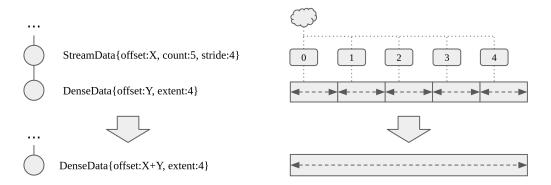

- Chapter 5 describes how techniques developed in Chapters 3 and 4 can be integrated transparently with existing MPI applications. This includes a novel low-overhead and general strategy for handling non-contiguous GPU data, low-latency use of empirical performance information at runtime to inform communication strategy, and an implementation that can transparently improve communication methods without modifying applications.

- Chapter 6 discusses related work.

- Chapter 7 offers conclusions and future directions for this work.

## Chapter 2

## Background

## 2.1 CUDA System

For the purposes of this document, a CUDA-enabled computer comprises three pieces: first, one or more CUDA "devices" – general-purpose graphics processing units (GPGPUS or usually GPUs). Second, the "host" – the CPU(s) and associated memory. Third, the "CUDA system" – the combination of the CUDA runtime library (accessible to the program through the CUDA runtime library), the CUDA driver (not directly controllable from the program), and the interconnect hardware (accessible through the operating system).

The host and devices are where the traditional focus of high-performance computing has been, e.g. loop optimization, vectorized operations, branch prediction, and low-cost software abstractions. While these two components are crucial to application performance, so is the CUDA system itself. Within the CUDA system, the runtime library, driver, and interconnect hardware all contribute to the observable performance.

## 2.2 CUDA Runtime API vs. CUDA Operation

The performance of CUDA operations comprises two pieces: the time it takes the application thread to initialize the operation, typically by making CUDA runtime library calls, and the time it takes the CUDA system to execute the operation.

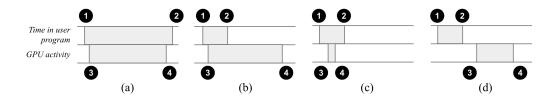

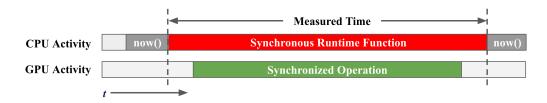

Figure 2.1 shows four scenarios: 2.1a, a synchronous operation, where control is not return to the program until the GPU activity is completed; 2.1b, an asynchronous operation, where the calling thread is blocked for long

Figure 2.1: Examples of time taken in the CUDA runtime and corresponding GPU activity. (a) A synchronous operation, (b) an asynchronous long operation, (c) an asynchronous short operation, and (d) a delayed operations.

enough to initialize the operations; 2.1c, an asynchronous operation where the operation is so short it completes before control returns to the calling thread; and Figure 2.1d, an asynchronous operation that is substantially delayed from the point of initiation. The interval **0**-**2** represents how long before control returns to the CPU (possibly to initiate another GPU operation), and **3**-**3** represents actual execution using the GPU resources. Depending on the API call and the operation, these intervals may be very different, though both intervals are relevant for understanding GPU performance.

## 2.3 CUDA Streams and Events

A CUDA stream is a queue of device work. With some exceptions for the default stream, each stream represents an independent queue whose contents is to be consumed by a GPU sequentially. Contents in different queues can be consumed by one or more GPUs in parallel. Within a stream, no operation may begin until the previous operation has completed. Between streams, there is no implicit ordering.

Streams are the main vehicle for task-level concurrency in single-GPU and multi-GPU systems. A single GPU can improve its utilization by pulling independent tasks from multiple streams. Multiple GPUs can have parallel tasks executing from multiple streams.

Kernels can be enqueued into a specific stream via their launch parameters. The cudaMemcpyAsync<sup>\*</sup> family of functions enqueues data transfer operations in a stream explicitly. A CUDA event can be inserted into a stream, and serves as a no-op that still maintains its position in the queue. Streams can be synchronized with the host through cudaStreamSynchronize, or with other streams independent of the host with cudaStreamWaitEvent. Finally, streams can have higher or lower priority. When a GPU can take an operation from a stream, it will pick an operation from a higher priority stream over a lower one.

## 2.4 Data Movement in CUDA Systems

This section describes the three classes of user-facing data transfers in CUDA systems: explicit transfers, zero-copy/mapped transfers, and managed memory.

#### 2.4.1 Explicit Block and Strided Transfers

Explicit transfers are initiated through the cudaMemcpy<sup>\*</sup> class of API routines. A contiguous buffer referenced by a pointer and a size is transferred from one address to another. GPUs include copy engines, which are able to handle these transfers without invoking the GPU SMs or the CPU. CUDA also provides similar APIs that allow transfers of non-contiguous memory regions through the cudaMemcpy2D<sup>\*</sup> and cudaMemcpy3D<sup>\*</sup> functions. Depending on the GPU hardware, these non-contiguous transfers place various restrictions on the size and alignment of the individual contiguous blocks of the non-contiguous object. Otherwise, these functions are similar to the explicit transfers described above.

#### 2.4.2 Zero-copy and Direct Access

"Zero-copy" is a common name for the ability of different devices to directly access memory which is physically present on another device. These accesses are served by a transaction over the interconnect, without changing the location of the backing data. Memory accesses originating from the CPU or GPU that reference data on another device are converted to requests that cross the interconnect (e.g. PCIe or NVLink). Data is retrieved from the owning device, and returned to the source device over the interconnect. These accesses are particularly high latency, and require very careful attention to alignment and coalescing to achieve full link utilization [29]. When this mechanism is used for accesses between the CPU and GPU, it is commonly called a "zerocopy" access, or an access to "zero-copy" memory. There is not a broadly accepted term for a GPU kernel accessing data on another GPU; in this document, it is referred to as "direct access" or "zero-copy".

#### 2.4.3 Unified Memory

CUDA optionally provides a unified memory abstraction, where the CUDA system is responsible for presenting a coherent image of memory to all devices, including atomic operations across the entire system. Such memory can be allocated with the cudaMallocManaged function. In order to accelerate performance, CUDA will try to move data at the page granularity to the device that most recently accessed it (the "demand" mechanism). It may also rely on the direct-access mechanism when thrashing access patterns are detected. The user can provide usage hints through the cudaMemAdvise API, including prefetching data to the device (the "prefetch" mechanism).

### 2.5 Synchronous and Asynchronous CUDA Operations

"Synchronous" CUDA operations are those which block progress on the calling CPU thread until they have completed. They are commonly used due to simpler integration with host code during the initial development process. For example, a compute-intensive CPU function (which is naturally blocking, as the caller does not proceed until the function returns) can be directly replaced with a synchronous GPU operation without changing the semantics of the application.

"Asynchronous" operations are those which do not block the calling thread. In this case, the calling thread will dispatch work to the GPU, and then proceed, and the GPU will execute that work at some point in the future. An example of such an operation is the cudaMemcpyAsync function, which starts a data transfer but may return before that transfer is complete. Use of these functions typically allows better utilization of GPU resources, but requires more complex coordination of CPU and GPU execution. Even when the primary interaction between the CPU and GPU is asynchronous, synchronous operations are always eventually used to make sure the host does not attempt to retrieve incomplete results from the GPU.

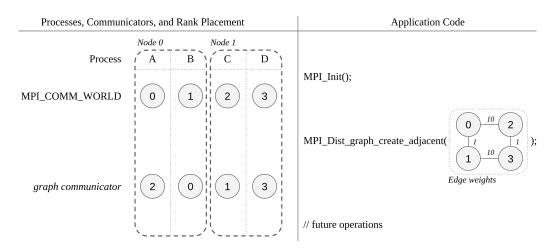

### 2.6 MPI

MPI is a specification for a library that implements the message-passing parallel programming model [30]. MPI implementations have become the dominant choice for distributed-memory high-performance computing on supercomputers. Several implementations are widely used, including Spectrum MPI [31], Open MPI [32], MPICH [33], and MVAPICH [34]. MPI functions operate on untyped buffers, which are typically "source" or "destination" buffers, or both. MPI includes a variety of point-to-point transfers and collective operations, and synchronous and asynchronous versions of most functions.

#### 2.6.1 CUDA-Aware MPI

CUDA does not directly provide a mechanism to move data between GPUs on different nodes. A common programming pattern on GPU-accelerated distributed computing is to use CUDA to manage data movement between GPUs and from CPU to GPU, and to use MPI to move data between CPUs. Some MPI implementations optionally support passing device pointers directly to MPI calls, leaving it up to the MPI implementation to handle moving data between GPUs in different ranks. Such implementations are said to be CUDA-aware MPI implementations.

# Chapter 3

## Measurements

The foundation for improving multi-socket and multi-GPU data transfer performance is measurement of the properties of that transfer. Comm|Scope [35] is a tool primarily developed by the author to address some of the pitfalls and gaps of previous measurement work. For a more detailed discussion of related work see Chapter 6. Comm|Scope contributes low-overhead bandwidth measurement implementations coupled with careful system performance controls. With detailed measurements, it is possible for users to adjust the design of their applications to maximize performance, and for system developers to observe minute effects that may point to performance bugs. This chapter describes the design and implementation of Comm|Scope, shows how CUDA achieves dramatically different bandwidth under different configurations, and describes guidelines for high-performance CUDA data transfer.

## 3.1 Comm|Scope Design

Comm|Scope [35] is a CUDA C++ microbenchmark program developed by the author that measures the performance of CUDA data transfers and associated API calls. It uses the libscope system benchmarking library, also developed by the author and described in Section 3.2.

#### 3.1.1 Low-overhead Bandwidth Measurement

Section 2.2 describes the contributions of the CUDA runtime and the rest of the CUDA system to the total execution time of CUDA operations. When measuring the raw bandwidth achievable over the link, Comm|Scope's microbenchmarks minimize the unintended measurement of CUDA runtime overhead. This section describes the measurement approach.

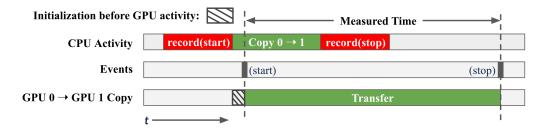

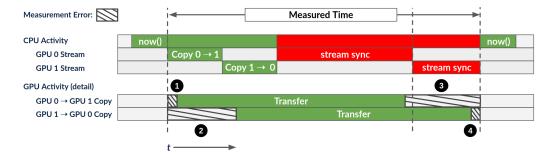

Asynchronous operations are best measured with CUDA events, which minimize the overhead of the measurement. Figure 3.1 shows an example timeline of measurement. An event is recorded at the beginning and end of one or more CUDA operations within a stream, and then the cudaEvent-GetElapsedTime function provides the time between the two events.

Figure 3.1: Example timeline of correctly measuring an asynchronous data transfer between GPU 0 and GPU 1. The CPU records a *start* and *stop* event on either end of the transfer. The CUDA system records when those events trigger in the stream, and cudaEventGetElapsedTime is used to measure the transfer time, without including initialization time on the CPU before the GPU activity begins.

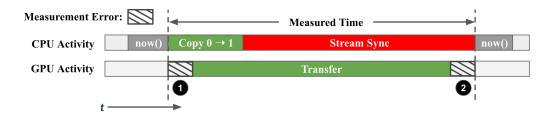

A common but less-accurate method is to use host wall-clock time with synchronous CUDA operations, or asynchronous CUDA operations followed by cudaDeviceSynchronize or cudaStreamSynchronize. Figure 3.2 shows an example of this method. It incorrectly includes two unknown times: the time between the function call and the start of the operation (①), and the time between the end of the operation and the end of the synchronization with the host (②). Even widely referenced benchmarks like SHOC [36] use this method. When Comm|Scope measures the time of asynchronous CUDA operations, it uses the low-overhead method in Figure 3.1.

#### 3.1.2 Bidirectional Transfer Measurements

The bidirectional bandwidth of a link is the amount of data that can be transmitted simultaneously in both directions in a specified amount of time. When the two transfers begin and end at the same time, the bandwidth is the total data amount divided by the elapsed time. In practice, using this approach to measure bidirectional bandwidth is challenging due to skew between the transfer start and stop times. It is also not possible to accurately

Figure 3.2: Example timeline of a less-accurate measure of asynchronous operation time. The host wall time (now) is recorded before and after the operation is launched. **0** (**2**) marks a duration when the CPU initiates (waits for) the operation and the operation actually begins (ends). In contrast to the procedure shown in Figure 3.1, these durations are incorrectly included in the measured time.

determine *only* the overlapping portion of the two transfers: CUDA events cannot be queried for an absolute start and end time, and elapsed time between events in different streams cannot be compared. An obvious but less-accurate approach is to record the wall time, initiate the asynchronous events, and then record the wall time again once both events have completed. Figure 3.3 shows a timeline of such a measurement.

Figure 3.3: Example of improper measurement of a bidirectional transfer. Before both transfers are initiated and after both transfers complete, the host wall time is used to infer the achieved bandwidth. **①** is skew between the CPU entering the CUDA runtime call and the beginning of the operation. **②** highlights how the second transfer can be delayed due to the CPU cost of initializing the first transfer. **②** shows how one transfer may end before the other. **③** is skew between the end of the operation and the CUDA runtime call returning. These measurement errors make the bidirectional bandwidth appear lower than its true value.

Two streams are used to allow the transfers to execute at the same time, with one in each stream. The CPU thread records the starting wall-time, initiates both transfers, synchronizes both streams, and then records the ending wall time. The weaknesses of this approach is that it introduces skew in the start  $(\mathbf{0})$ , stop  $(\mathbf{2})$ , and includes time between the end of the operation and return of control to the host thread  $(\mathbf{3} \text{ and } \mathbf{3})$ . All these errors improperly reduce the estimate of the bidirectional bandwidth, as the links are not fully active during the measured time.

Comm|Scope minimizes the effect of the start-time skew and synchronization overhead (① and ③ in Figure 3.3) through a corrected measurement implementation, shown in Figure 3.4.

Figure 3.4: Example of an accurate measure of a bidirectional transfer. One direction is associated with each stream. First, a busy-wait kernel is launched to block operations from beginning during initialization. The "start" event is used to synchronize the beginning of the operations in each stream, and a "done" event is used to mark when both operations have completed. In this manner, the "start" and "stop" events bookend both transfer options with minimal overhead.  $\bullet$  is skew when the actual transfers do not take the same amount of time, and therefore are not fully overlapped.

Before the measurement begins, a busy-wait kernel is launched in the first stream. This kernel occupies the GPU, and the CUDA event *start* inserted afterwards is used to block the execution of the two data transfers until the kernel completes. The run-time of the wait kernel is sufficient to allow the CPU to set up all asynchronous transfers and events, thereby removing the start-time skew. This is ensured by querying whether the *start* event has been triggered after all communications are initialized. If so, the kernel was no long enough, and the process is restarted with a longer wait kernel. This is ensured by progressively lengthening the kernel until it has not completed after the CPU Since CUDA events in different streams cannot be compared for elapsed time, the *stop* event in the first stream waits for the *done* event in the second stream. The result is that *start* marks the time the transfers begin, and *stop* is only recorded once both transfers have ended. The synchronization overhead is removed by using cudaEventGetElapsedTime to measure the transfer time. **1** may still occur if one transfer is slower than the other.

#### 3.1.3 Measuring Synchronous Operations

Synchronous CUDA operations do not return control to the calling thread until they are complete. Comm|Scope measures synchronous operations by using the wall-time before and after the operation. Figure 3.5 summarizes the technique.

Figure 3.5: Example of an accurate measure of a synchronous operation. The purpose of the synchronous operation is to block the calling thread, so the measured time is simply the length of time the calling thread is blocked.

### 3.2 Libscope Design

Libscope is a C++ system benchmarking library, developed by the author, which brings a variety of pre-existing techniques under one umbrella to ease the implementation of CUDA microbenchmarks that are sensitive to system configuration. This section describes the techniques implemented in libscope.

#### Variable CPU Clock Speeds

Many computers feature dynamic CPU frequency scaling to conserve power when idle and boost performance for transient tasks. This presents a challenge when measuring performance, as CPU frequency may not be the same from run to run. In the context of this work, the CPU performance could have a substantial impact on performance of the CUDA unified memory system and CUDA driver operations. On Linux, libscope automatically sets the CPU governor to "performance" and can disable CPU boosting through the ACPI or Intel P-State [37] interface. The original CPU scaling behavior is restored when the benchmarks exit or are interrupted. Prior CUDA communication benchmarks make no report of whether or how this variable is controlled.

#### CPU Data Caching

CPU caches have a measurable effect on CPU/GPU data transfer performance. Libscope provides an interface for flushing CPU caches through the dcbf [38, p. 773] on POWER and clflush [39, p. 139] on AMD64. These instructions invalidate and flush the cache lines associated with a particular virtual address from all CPU data caches. This is done in some Comm|Scope benchmarks before the transfer is initiated. Prior works that measure CUDA transfers do not address this consideration.

#### 3.2.1 NUMA Pinning

In ordinary program execution, the operating system may move the program between CPU cores or sockets. This introduces execution time variability by causing cache misses and changing which interconnects are required to move data between the CPU and GPU. Libscope uses libnuma [40] to control the execution and memory allocation pinning to specific sockets or CPUs in order to control which interconnects are measured.

#### 3.2.2 Compiler Side-Effects

When measuring zero-copy or unified memory host-to-GPU performance, the GPU kernel should be as close to pure reads as possible to ensure that host-to-GPU data delivery is measured with as little overhead as possible. Listing 3.1: Minimal GPU read kernel (not implemented).

```

template <unsigned GD, unsigned BD, typename read_t>

1

2

__global__ void gpu_read(const read_t *ptr,

3

const size_t bytes) {

4

const size_t gx = blockIdx.x * BD + threadIdx.x;

5

const size_t num_elems = bytes / sizeof(read_t);

6

7

for (size_t i = gx; i < num_elems; i += GD * BD) {</pre>

8

read_t t;

9

t = ptr[i];

10

}

11 }

```

Listing 3.1 shows such a minimal kernel. The grid of threads (grid size GD and block size BD) loops over bytes bytes pointed to by ptr, loading them with read\_t accesses. When the benchmarks are compiled with optimizations turned on, the compiler observes that the load implied by line 9 has no effect, and the entire code is eliminated, preventing the load performance from being measured.

To correct this, the code is modified in two ways, shown in Listing 3.2. First, the do\_not\_optimize function is called on the result of the load. do\_not\_optimize is a wrapper that inserts PTX code which puts a fake data dependency and memory side-effect on the argument. This does not insert any instructions, but prevents the compiler from removing the unused load in the generated PTX code.

Unfortunately for benchmarking (but fortunately when generating optimized application code), the second phase of the compilation which transforms the PTX code into SASS will also do some simple optimization. In this case, it will observe that the virtual register corresponding to t is unused, and remove it (along with the load that generated it, which is the target of the measurement). To defeat the second optimization, the flag parameter is added, and a dummy store is hidden behind a conditional predicated on the value of flag. This prevents the compiler from statically removing the load. At run-time, this flag is given a null pointer, so the dummy store is not executed. However, the compiler can still observe that the load only has an effect if the store occurs (if flag is true), and lowers the load into the conditional body guarded by flag. The do\_not\_optimize function also prevents this from occurring. Listing 3.2: gpu\_read kernel

```

1 template <unsigned GD, unsigned BD, typename read_t>

2

__global__ void gpu_read(const read_t *ptr, read_t *flag,

3

const size_t bytes) {

4

const size_t gx = blockIdx.x * BD + threadIdx.x;

5

const size_t num_elems = bytes / sizeof(read_t);

6

7

for (size_t i = gx; i < num_elems; i += GD * BD) {</pre>

8

read_t t;

9

do_not_optimize(t = ptr[i]);

10

if (flag) {

11

*flag = t;

12

}

13

}

14 }

```

Listing 3.3 shows two implementations of do\_not\_optimize for different argument types. Since they are template \_\_device\_\_ functions, they are inlined and there is no function call overhead.

Listing 3.3: device do\_not\_optimize

```

1 template<> __device__

2 void do_not_optimize<int32_t>(const int32_t& t) {

3 asm volatile("" :: "r"(t) : "memory");

4 }

5

6 template<> __device__

7 void do_not_optimize<int64_t>(const int64_t& t) {

8 asm volatile("" :: "l"(t) : "memory");

9 }

```

## 3.3 Observations and Guidelines

Systems-oriented microbenchmarking can accurately quantify data transfer performance, reveal subtleties of performance not previously described in the literature, and reveal surprising behavior that might suggest performance bugs. This section highlights some examples from the leadership-class Summit system at Oak Ridge National Lab.

In particular, the measurements highlight:

- The large difference in observed data transfer performance depending on which data transfer method is used:  $2 \times$  for GPU-GPU,  $8 \times$  for GPU-CPU (Section 3.3.2).

- How locality improves bandwidth bandwidth (Section 3.3.3).

- How bidirectional transfers improve link utilization (Section 3.3.4).

- How multiple threads cannot hide CPU cost (Section 3.3.7).

- Using the CUDA Graph API to reduce CPU cost (Section 3.3.7).

#### 3.3.1 Experimental System

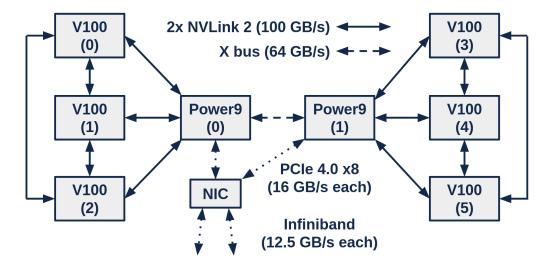

All experiments for this chapter are carried out on Summit [41], a leadershipclass computing system at Oak Ridge National Labs. Summit comprises 4,600 compute nodes, each summarized in Table 3.1 and Figure 3.6. Triplets of GPUs are associated with each CPU: GPUs 0-2 with socket 0 and GPUs 3-5 with socket 1. Within a triplet, components are fully connected by NVLink 2.0 x2 links, for 100 GB/s bidirectional bandwidth. Between triplets, the sockets are connected with a 64 GB/s x-bus SMP interconnect. This means that communication localized to one triplet should be at much higher bandwidth than communication between triplets. The network is a non-blocking fat tree of EDR InfiniBand with 23 GB/s node injection bandwidth [42].

Figure 3.6: Diagram of interconnect bandwidths of a Summit compute node.

#### Table 3.1: Summit node hardware summary

CPU

OS

Kernel

GPUs

CUDA Driver

MPI

nvcc

cc

22-core POWER9

RHEL 7.6

4.14.0-115.21.2.cl7a.ppc64le

V100-SXM2-16GB

418.116

Spectrum 10.3.1.2

10.1.243

g++ 6.5.0

#### 3.3.2 Bandwidth Utilization

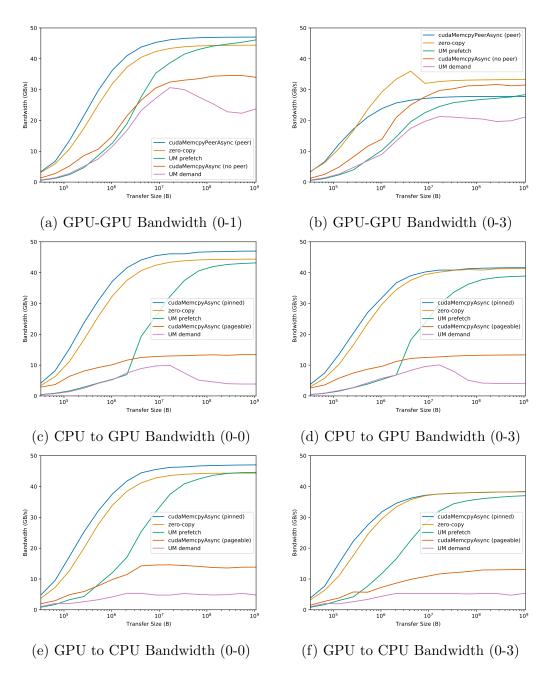

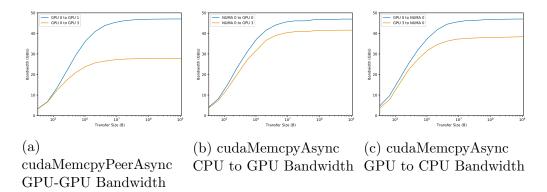

CUDA provides a variety of methods for moving data between participating components, and not all provide the same performance. For example, five methods for moving data (explicit transfers with and without peer access, zero-copy access, and unified memory through the demand or prefetch mechanism) between components are compared in Figure 3.7. All transfers are unidirectional. Figures 3.7a, 3.7c, and 3.7e show "near"-component bandwidth (directly connected CPUs and GPUs), and Figures 3.7b, 3.7d, and 3.7f show "far"-component bandwidth (CPUs and GPUs associated with different sockets). Several observations are apparent:

- For "small" sizes (<  $10^6$ ), elapsed time is dominated by a fixed overhead.

- For "large" sizes (>  $10^8$ ), elapsed time is dominated by the transfer size.

- Larger transfers typically have greater-or-equal bandwidth to smaller transfers of the same type.

- No transfer reaches the 50 GB/s theoretical "near" limit (the fastest is 94%).

- The x-bus is nominally 64 GB/s bidirectional [43], but certain "far" transfers are able to exceed 50% of that speed, reaching 40 GB/s.

- zero-copy transfers can reliably match explicit transfers for favorable access patterns. The gap in Figures 3.7a 3.7e is probably due to a small amount of overhead introduced by interaction with the cache. For the slower "far" transfers, the interconnect is slow enough to mask the effect.

- Section 3.3.3 highlights the locality effects.

It is clear that the achievable bandwidth depends strongly on the modality, i.e. the method used. The variation of achievable bandwidth can be up to 2x for GPU-GPU transfer.

Figure 3.7: GPU-GPU and GPU-CPU bandwidth for different CUDA transfer methods. Numbers in parentheses, e.g. (0-1), refer to the participating CPU or GPU ids. For each row, all transfers occur over the same links, but the CUDA communication method can strongly affect performance.

#### 3.3.3 Locality

Section 3.3.1 described how different components have different theoretical bandwidth between them. These bandwidth differences have a strong effect

on bandwidth measurable at the application level. Figure 3.8 highlights a specific transfer method from Figure 3.7 to demonstrate the locality effect between a pair of GPUs (3.8a), CPU-to-GPU (3.8b), and GPU-to-CPU (3.8c). For all transfers over NVLink, the system achieves 47.0 GB/s out of the theoretical 50 GB/s provided by the interconnect. For other transfers over x-bus, bandwidth drops. GPU-GPU transfers achieve 27.8 GB/s, while GPU  $\rightarrow$  CPU achieves 38.4 and CPU  $\rightarrow$  GPU achieves 41.6. The specifications for the x-bus are 64 GB/s bidirectional, but the CPU-GPU transfers achieve more than 50% of that capacity. This suggests the X-bus boosts its transfer rate when only a single direction is used (e.g., by increasing clock speed).

Similar effects can be seen for zero-copy and unified-memory prefetch transfers, the other two "fast" transfer methods.

Figure 3.8: GPU-GPU and GPU-CPU bandwidth. Data transfers over multiple interconnects (Section 3.3.1) exhibit lower bandwidth due to the lower x-bus bandwidth.

In summary, for CPU-GPU transfers, the performance effect of locality is less than expected since the unidirectional transfers achieve more than 50% of the bidirectional bandwidth. At most, CPU-GPU locality only affords a 23% bandwidth improvement. For GPU-GPU transfers it is important to place data so that larger communication occurs between directly connected GPUs, with directly connected GPUs having a 69% bandwidth improvement.

#### 3.3.4 Bidirectional Transfers

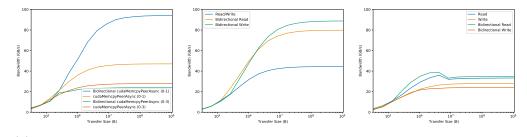

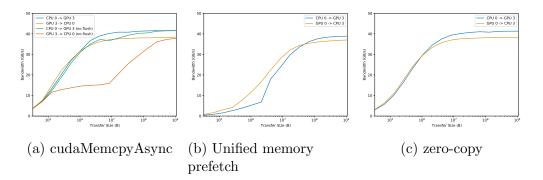

Typical interconnects have a higher bidirectional bandwidth than singledirectional. This is due to the physical construction of these bidirectional interconnects, which comprise pairs of single-directional physical links. Figure 3.9 shows how utilizing both directions of the link simultaneously typically improves aggregate bandwidth. Figure 3.9a shows the performance of cudaMemcpyPeerAsync. Figure 3.9b shows the performance of direct accesses between GPUs 0 and 1. Figure 3.9c shows the performance of direct accesses between GPUs 0 and 3, across the X-bus between two sockets.

(a) cudaMemcpyPeerAsync bandwidth. Bidirectional bandwidth drops for "far" transfers, but doubles for "near" ones. (b) Zero-copy (GPUs 0 to (c) Zero-Copy (GPU 0 to 1). Minor bandwidth 3). Bidirectional write variability in bidirectional accesses are slower than transfers is observable any unidirectional between near and far transfer. Bidirectional accesses, but both greatly read offers some small increased the total improvement. bandwidth.

Figure 3.9: Bidirectional transfer bandwidth for cudaMemcpyPeer, and zero-copy transfers between GPUs. For "far" transfers, bidirectional transfers cause a large bandwidth regression for cudaMemcpyPeerAsync and zero-copy transfers. For "near" transfers, performance nearly doubles, as expected. It is possible that some performance bug affects inter-socket transfers, or perhaps the X-bus boosts its transfer rate when only a single direction is used (e.g., by increasing clock speed).

#### 3.3.5 Cache Effects

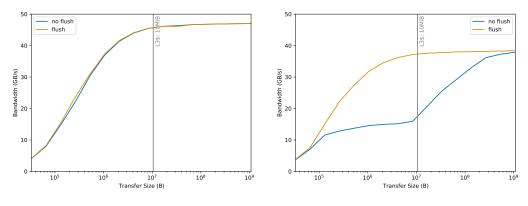

The state of the CPU cache affects the performance of GPU-to-CPU transfers. Figure 3.10 shows how remote GPU-to-CPU bandwidth varies when the L3 cache is flushed. When the cache is flushed, bandwidth for data coming to the CPU is greatly increased around the L3 cache size. This is probably because the cache does not need to be flushed on-demand. In a small unflushed transfer, each line in the destination buffer maps to a unique line in the cache. For a larger transfer, multiple addresses in the destination

(a) GPU 0 to NUMA 0 (single-hop) (b) GPU 3 to NUMA 0 (multi-hop)

Figure 3.10: GPU-to-CPU transfer bandwidth on a Summit node using cudaMemcpyAsync. When the CPU caches are flushed before the transfer, bandwidth is much higher for transfers around the L3 cache size (10MiB per core-pair).

buffer correspond to each cache line, which only needs to be invalidated once. As the transfer grows, the cost of each invalidation is amortized over many transferred bytes, and the bandwidth climbs back towards the maximum  $^1$ .

#### 3.3.6 Anisotropy

Anisotropy is the property of exhibiting different properties in different directions. In this context, it means that the bandwidth between two components is different in different directions.

This is observed on Summit for some transfers that cross the CPU socket boundary (e.g., between GPUs 0 and 3). This observation is not directly actionable for the user, as applications do not typically offer any flexibility in which direction data must move between the CPU and the GPU. System developers, however, may use these observations as a starting point to investigate performance bugs.

Figure 3.11 shows this effect in three scenarios. Figure 3.11a shows that CPU 0 to GPU 3 is several GB/s faster than the reverse direction. The effect is greatly magnified if the CPU cache is not flushed before receiving the data. Figure 3.11b shows that during unified-memory prefetch, smaller messages are faster in the GPU-to-CPU direction, while the opposite is true

<sup>&</sup>lt;sup>1</sup>The locality effect (Section 3.3.3) is also visible.

Figure 3.11: Examples of anisotropy in multi-hop intra-node bandwidth. Similar effects are not observed for directly connected components.

for messages larger than  $4 \times 10^7$  bytes. Figure 3.11c shows that for zerocopy transfers, the CPU-to-GPU direction is faster for messages above several dozen kilobytes. The GPU-to-CPU direction is stores instead of loads, which may incur some overhead for cache coherency.

#### 3.3.7 CUDA Runtime

Until now, this chapter was concerned with the achievable bandwidth across component links under various conditions. Comm|Scope can also be used to measure the CPU cost of invoking the runtime operations themselves. The high theoretical interconnect bandwidths mean that even a relatively fast runtime operation represents a large amount of data movement. Table 3.2 shows the cost of select CUDA runtime operations, and the maximum of data that could be moved in that time between two GPUs on a Summit node. For smaller transfers, the cost of initiating the transfer may dwarf the time of the transfer itself. To hide this cost, large transfers should be initiated before small ones to keep the CUDA system busy.

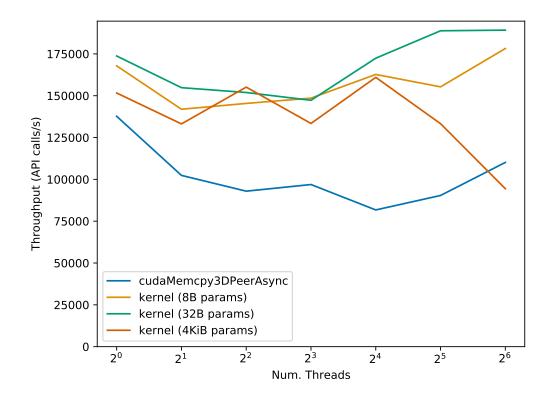

Comm|Scope also shows that using multiple threads to overcome this CUDA runtime cost is not effective. Figure 3.12 demonstrates this effect for various CUDA runtime operations. As the number of threads increases, the aggregate throughput does not substantially improve (and even degrades). Multiple threads controlling a GPU context introduce mutual exclusion locks, which causes the run-time cost of each call to grow. These measurements suggest that using multiple threads to control the GPU is not generally an appropriate method to issue CUDA runtime operations faster. Multiple threads

| CUDA Runtime Call       | Time (s)               | Bytes $(50 \text{ GB/s})$ |

|-------------------------|------------------------|---------------------------|

| cudaMemcpyAsync         | $5.169 \times 10^{-6}$ | $2.58 \times 10^5$        |

| cudaMemcpy3DPeerAsync   | $6.188 \times 10^{-6}$ | $3.09 \times 10^5$        |

| kernel launch $(0B)$    | $5.887\times10^{-6}$   | $2.94 	imes 10^5$         |

| kernel launch $(1B)$    | $6.093\times10^{-6}$   | $3.05 \times 10^5$        |

| kernel launch (256B)    | $6.064\times10^{-6}$   | $3.03 	imes 10^5$         |

| kernel launch $(4096B)$ | $6.595\times10^{-6}$   | $3.30 \times 10^5$        |

Table 3.2: Cost of select CUDA runtime operations on CPU 0, and how much data could be moved at 50GB/s during that time.

may be useful if other CPU work is the bottleneck instead of CUDA runtime throughput.

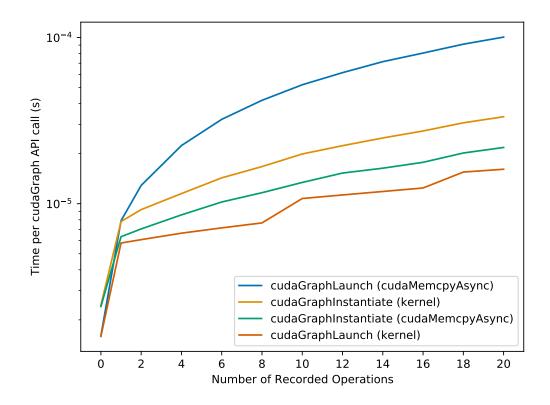

Another way to reduce the CPU cost of some CUDA operations is the CUDA graph API. CUDA Graph permits a two-step process, where a sequence of calls are "instantiated" (recorded), and then "launched" (replayed) later with reduced overhead. Any captured kernels are configured once, allowing future execution of the same kernel with the same arguments to be faster. This is especially useful if the same sequence of operations will be repeated over and over again. Figure 3.13 shows the run-time cost of the two CUDA Graph operations with a variable number and type of CUDA run-time calls. Using cudaGraphLaunch for kernels provides substantial speedup  $(7.6 \times \text{ at } 20 \text{ kernels}, \text{ compared with Table 3.2}).$

### 3.4 Conclusion

This chapter describes the design and implementation of Comm|Scope, a point-to-point communication microbenchmark for multi-GPU multi-socket systems. Two trends have combined to make intra-node bandwidth increasingly difficult to understand. First, improving performance of the underlying interconnect hardware causes other overheads (e.g. cache effects) to become apparent. Second, as systems become more heterogeneous, the interconnects between components become more non-uniform.

This chapter began by introducing the techniques that allow detailed measurements (Section 3.1). Synchronous and asynchronous CUDA operations are handled differently, as are unidirectional and bidirectional transfers. Once detailed measurement methodology is established, small sources of variabil-

Figure 3.12: Aggregate throughput of selected CUDA runtime calls with various numbers of calling threads (higher is faster). "params" refers to the total number of bytes in the CUDA kernel arguments. A large jump in cost is observed from one to two threads. As the number of threads further increases, some calls show performance rising back to the single-thread case, while other calls degrade further.

ity become visible. A separate library, LibScope, brings techniques together to manage variable CPU clock speeds, CPU data caching, NUMA pinning, and selectively defeat some compiler optimizations that inhibit benchmarking (Section 3.2).

Finally, the chapter concludes by presenting quantitative results, and some corresponding qualitative guidelines (Section 3.3). First, on fast interconnects, the choice of communication method is especially important. For GPU-GPU transfers, the fastest method (explicit) is more than double the speed of the slowest (unified memory demand accesses) due to the page-ownership mechanism required by the latter. For CPU-GPU transfers, that difference grows to roughly  $9 \times$  due to the CPU's inability to generate enough demand accesses to saturate the interconnect. On heterogeneous systems, GPU locality is important, with "nearby" GPUs featuring a 69% bandwidth

Figure 3.13: Cost of cudaGraphInstantiate (record) and cudaGraphLaunch (replay) when various numbers of runtime calls are captured. cudaGraphInstantiate is a one-time cost, and cudaGraphLaunch is incurred each time the sequence of operations is executed. cudaGraphLaunch provides no speedup for most runtime calls, but a  $7.6 \times$  speedup for launching 20 kernels.

improvement over "far" GPUs.

Some detailed measurements are more relevant for system integrators than application developers. When the CPU cache is flushed, GPU-to-CPU transfers can be doubled for sizes around the L3 cache size. Also measurable is "anisotropy," where the same transfers in different directions have different performance. This observation is typically not relevant for applications, but may allow system developers to identify unexpected performance behavior.

Comm|Scope can also be used to measure some aspects of the CUDA runtime performance. Specifically, this chapter addresses the cost of initiating certain device operations, as well as attempts to amortize that cost with the cudaGraph API (successful), and OS threads (unsuccessful).

This chapter focused on the performance of the OLCF Summit platform specifically. Discussion of additional platforms can be found in Pearson et al. [35]. The Appendix describes how to retrieve the Comm|Scope code (and libscope) source code. In Chapter 4, the lessons from Comm|Scope are integrated into a 3D stencil library. Chapter 5 attempts to generalize to arbitrary MPI applications, and also shows how some of the quantitative results can be used in an MPI implementation. Section 7.2.1 discusses extending Comm|Scope to intra-node communication.

# Chapter 4

# 3D Stencil Halo Exchange Library

This chapter describes how the results obtained in Chapter 3 inform the design of HPC stencil codes for heterogeneous computers. It also evaluates the effect of the design and explores how the design decisions can be automated, so application developers do not need to be experts in system configuration to achieve high performance.

- Fastest communication: heuristically select a fast communication method based on participating GPUs.

- Minimize run-time: use CUDA graph API to minimize CUDA kernel launch cost.

- Minimize run-time: use a single thread per rank to control GPU.

- High link utilization: all communication happens asynchronously.

- High link utilization: longer transfers before shorter, to overlap transfer with initiation.

In addition, the code makes the following algorithm-level optimizations that synergize with the system-level communication optimizations above:

- Hierarchical spatial decomposition to minimize communication.

- Elision of unneeded halo exchanges based on stencil kernel "shape".

Furthermore, the library automatically handles indexing to simplify

- Accessing memory from GPU kernels through grid coordinate.

- Overlapping GPU kernel execution with distributed data transfer.

This chapter motivates, describes, and evaluates a patch-based distributed stencil library developed by this author and first introduced in Pearson et al. [44]. Consideration is restricted to stencil codes on homogeneous systems, i.e., each group of individual resources has the same characteristics. This is consistent with a typical execution on current high-performance computing platforms, and sidesteps any complications from externally-imposed resource contention or a changing execution environment. Given these preconditions, the system properties can be measured once, and an effective static communication strategy can be created. It is possible that a static environment with different architectures and/or endianness on sending and receiving nodes could be created, while still maintaining similar performance characteristics. While this chapter and the next do not explicitly address that case, the discussion and findings still apply.

The rest of this chapter is organized as follows. Section 4.1 describes a general CUDA+MPI distributed stencil code. Section 4.2 describes challenges of using CUDA+MPI directly to implement the stencil halo exchange. Sections 4.3, 4.4, and 4.5 describe how the stencil library implements a fast CUDA+MPI halo exchange. Section 4.6 evaluates the library in the context of the Astaroth stencil code. Finally, Section 4.7 concludes.

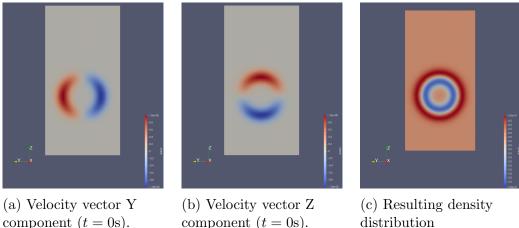

## 4.1 Distributed Stencil Overview

Stencil computation is a fundamental formulation for solving differential equations using finite difference, finite volume, and finite element methods, which are used widely in high-performance computing (HPC) applications such as simulating fluid dynamics, magnetohydrodynamics (MHD), space weather predictions, seismic wave propagation, and others. The application domain is represented as a discrete grid; stencil codes iteratively update each gridpoint based on some function of its local neighborhood. The stencil *kernel* (distinct from GPU kernels) describes the weights that each quantity from the neighboring grid points contributes to the new value of the produced gridpoint.

Each gridpoint may have several *quantities* associated with it (e.g. temperature, pressure, partial derivatives, etc.). Each quantity is typically stored in an "structure-of-arrays" style, rather than interleaving the quantities for each gridpoint in a "array-of-structures" style. This can assist with efficient memory access during vectorization, as the same quantities for multiple gridpoints are contiguous in memory and can be accessed in a single large load or store. Furthermore, separate allocations also ensure that alignment requirements for different datatypes are met.

Modeling phenomena with high spatial and/or temporal resolution leads to enormous stencil grids. Current large-scale CPU simulations use up to  $10^{10}$  grid points and  $10^5$  CPUs [45, 46], and are still orders of magnitude too small to capture phenomena of interest in available time and energy budgets. This has led to interest in using GPUs for stencil applications.

GPUs excel when there is limited data exchange, structured data reuse, and massive parallelism. Stencils exhibit all of these properties [47]. Once the stencil data is initialized on the GPU, it remains there without further exchange with the host. The data-reuse between neighboring gridpoints is (relatively) easy to leverage through shared memory and register queues in GPU kernels, and the grid points can be updated in parallel.

For large-scale stencil applications, the grid data may be much larger than a single GPU's memory. Recent stencil codes use 1-8 quantities, a typical stencil radius of 3, and subdomains per GPU of  $512^3$ , with a total domain size of around  $10^{10}$  at most [47, 48, 49, 50].

Typically, the stencil grid is spatially decomposed into *subgrids*, which are placed in different memories. In each iteration, the exterior "shell" of these subgrids needs gridpoint values that are located in different memories. An explicit halo-exchange is used, where each subgrid includes a perimeter of *ghost points* representing grid points from neighboring regions. During each iteration, these ghost cells are updated with the new value from the corresponding neighboring subgrid. This update is called the *halo exchange*, and is the main focus of this chapter. These ghost gridpoints for the neighboring subgrid are stored in the same allocation as the real gridpoints, preserving locality for the stencil computation and keeping memory access regular during local computation.

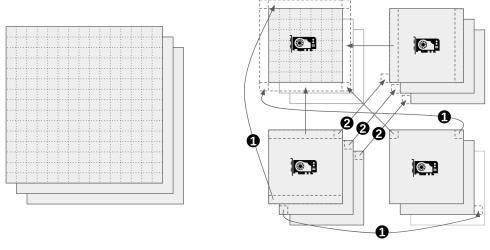

Figure 4.1 shows an example of a distributed stencil. Figure 4.1a shows a full stencil grid with three quantities. In Figure 4.1b the grid is split among four GPUs, with each GPU holding all three quantities of a subgrid. Gridpoints near the edges in one subgrid are reflected as the ghost points of neighboring subgrids. Each quantity only exchanges with the corresponding

(a) Full stencil grid.

(b) Decomposed stencil grid with ghost points.

Figure 4.1: A stencil grid with three quantities distributed among four GPUs. Data from one subgrid is sent to the ghost region of the neighboring subgrid. Some exchanges reflect periodic boundary conditions  $(\mathbf{0})$ . Exchanges are done on a per-quantity basis  $(\mathbf{2})$ .

quantity in neighboring subgrids (@). Communications may "wrap" around the grid perimeter (①) for periodic boundary conditions.

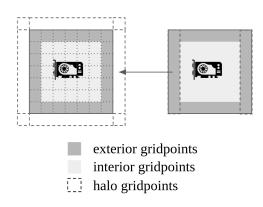

In this construction, there is a large amount of parallelism available. At a high level, the gridpoints allocated in each subgrid can be divided into three groups. The largest are interior gridpoints. The values needed to produce these points are entirely owned by the subgrid, and are not among the ghost gridpoints. An outer shell of exterior gridpoints is also owned by the subgrid, but cannot produce new values until the values from the neighbors arrive in the ghost points. The thickness of this shell is defined by the order of the stencil function.

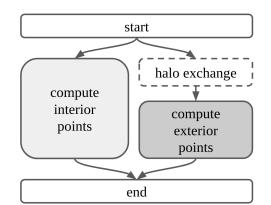

The values for interior gridpoints may be computed immediately when the iteration starts, as the subgrid already contains all values needed for them after completion of the previous iteration. Since the interior points do not need the ghost points, the halo exchange can also immediately begin in parallel. Once the halo exchange has completed, the exterior points can be computed. Figure 4.2 summarizes this.

Fine-grained parallelism is available in the halo exchange. Each halo exchange can be broken up into  $N_{quant} \times N_{dir}$  independent and parallel messages, where  $N_{quant}$  is the number of quantities and  $N_{dir}$  is the number of directions.

(a) Diagram of exterior, interior, and ghost gridpoints.

(b) Dependency graph for halo operations. Interior gridpoints may be operated on while halo exchange or exterior gridpoint kernels are running.

Figure 4.2: Dependency graph for stencil operations. Interior gridpoints only have a dependency on gridpoints already in the local subgrid. Exterior gridpoints require values from the ghost points to produce new values. The ghost gridpoints are provided by neighboring subgrids during halo exchange.

Likewise, the exterior gridpoints can be correspondingly divided into groups according to which ghost points they need from which messages. These exterior gridpoints could be launched immediately when the corresponding ghost points are received, without waiting for the entire halo exchange to complete.

## 4.2 Challenges with CUDA+MPI Stencil Codes

Emerging distributed HPC clusters feature nodes of multi-socket CPU and multiple GPUs, with CUDA and MPI libraries to exploit the hardware. These libraries are relatively low-level, featuring fine-grained control of the underlying platform and many options for communication and data allocation. Thus, implementing high-level data placement and communication strategies for large-scale stencil computations on such clusters is a challenging task.

Computational parallelism is straightforward to capture through GPU kernels (though much work is devoted to optimal implementations for various cases). The challenge from a systems perspective comes from highperformance combination of GPU and MPI communication primitives to facilitate data movement through the heterogeneous system. This design is informed by careful measurement of the primitives (Chapter 3).

In the last decade, CUDA-aware MPI implementations have allowed GPUresident data to be passed to MPI operations. This simplifies CUDA+MPI applications, as the developer no longer needs to manage CPU-GPU data transfers. GPUDirect [51] has promised to accelerate these operations by allowing GPUs and NICs to interact directly without staging data through the CPU. Despite that, careful use of user-facing functions can surpass the performance of these abstractions.

MPI does not feature a primitive that directly maps to stencil communication, though it does offer some building blocks. MPI datatypes can be used to describe the (mostly) non-contiguous data that needs to be exchanged between subgrids (this is discussed further in Section 5.1.3). This allows application code to operate above the abstraction of messaging with individual bytes, which simplifies the code and allows the MPI implementation to provide high-performance handling of non-contiguous types. There would be at least one datatype per equivalent halo region. For example, depending on how the MPI communication routines are invoked, the +x and -x face (the subgrid surfaces whose normal vectos are the positive and negative directions of the x-axis) may be able to share the same MPI derived datatype but operate with different starting addresses.

MPI collectives allow all participating ranks to send at most a single message to all other ranks. The simplest form (MPI\_Alltoall) restricts all ranks to send/receive the same count and type of data to all other ranks. MPI\_Alltoallv allows each rank to send/receive a different count from each rank, and MPI\_Alltoallw further relaxes each rank to send/receive a different type from each other rank. When combined with derived datatypes, MPI\_Alltoallw is the most natural collective to use, as each rank can exchange the corresponding halo region datatype with the corresponding neighboring rank. MPI\_Alltoallv can be used if MPI\_Pack/Unpack is first used, explicitly transforming each non-contiguous datatype into a flat buffer of MPI\_TYPE\_PACKED. MPI\_Alltoall can only be used if a separate MPI\_Alltoall call is used for each different size message.

Unfortunately, all collectives only allow data to be sent/received from a single source/destination buffer, meaning that if quantities are stored in separate allocations, then multiple collectives must be used. Furthermore, in

stencils with periodic boundary conditions, a pair of ranks may need to exchange data along more than one "direction". This is distinct from the common case, where two ranks would exchange a single halo region in a single direction. This can be handled by using MPI\_Pack and MPI\_Unpack to place multiple datatypes into a single buffer, or by building an MPI\_Struct type to combine the two types.

Furthermore, stencil is not a good fit for collectives because most ranks will not exchange data. For example, in a 3D stencil, each subgrid will have at most 26 neighbors regardless of how many ranks are present. For very large decompositions, substantial time in the collective call can occur iterating over ranks that exchange no data. MPI introduced "topologies" to handle this case. First, the MPI Cartesian topology simplifies determination of neighboring ranks in a regular grid. It only operates directly on coordinate directions, but through multiple directional shifts (e.g. up, then left), diagonal ranks can also be determined. MPI graph topologies likewise allow the construction and query of arbitrary neighbor relationships. For each topology there is a collective operation corresponding to the ones described above, where only neighbors participate. Theoretically, this fixes the sparsity in the collectives.

These obstacles have driven many attempts to create distributed stencil communication frameworks. Fundamentally, the library described in this work represents a comprehensive effort to automate, combine, and evaluate partially realized communication techniques used in previous stencil works. Compared to prior work, it introduces automatic communication specialization, flexibility under mappings of GPUs to MPI ranks, and evaluation of the communication performance specifically thanks to these techniques. It combines those techniques with benchmark-driven design, node-aware data placement and communication overlapping. See Chapter 6 for a more thorough discussion of related work.

## 4.3 Grid Partitioning

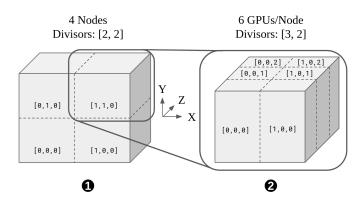

The stencil library uses a two-level hierarchical recursive bisection algorithm common for this type of problem [52, 53]. Consider a system with N nodes and P GPUs per node. First, the stencil grid is evenly partitioned into N

node-level subgrids to minimize the total off-node communication volume. The algorithm ensures these subgrids are as cubical as possible, minimizing the exterior-to-interior (Section 4.1) volume, and therefore the required internode communication per gridpoint.

The same algorithm is applied to each node-level subgrid to further subdivide it into P GPU-level subgrids, again minimizing the exterior-to-interior volume ratio and the required *inter-GPU* communication (subject to the already minimized inter-node communication).

Figure 4.3: Hierarchical partitioning of the stencil grid into node-level subgrids ( $\mathbf{0}$ ) and further into GPU-level subgrids ( $\mathbf{0}$ ). In this example, four nodes are partitioned into 2x2 along the X and Y dimensions. The resulting subgrid is partitioned among six GPUs by 3 in the z dimension and 2 in the x dimension. Each partition has a three-dimensional node and GPU index.

Figure 4.3 shows an example of the hierarchical decomposition of a stencil grid for four nodes with six GPUs per node (N = 4, P = 6). First, the recursive bisection scheme is applied to the whole grid at the node level ( $\mathbf{0}$ ). The grid is largest in the x-dimension, so the grid is divided by the largest prime factor of 4, which is 2. After that division, y is the largest dimension, so the grid is further divided by the next prime factor, again 2. This yields four subgrids, each with a three-dimensional node index. The exterior volume of these subgrids is minimized given the requirement of four equally sized subgrids.

Then the recursive bisection is applied to each node subgrid at the GPU level (2). For six GPUs, the prime factors are three and two. The longest dimension of the node subgrid is z then x, so the node subgrid is divided along those axes by three and two, respectively, to yield the subgrids that will be assigned to each GPU (Section 4.4).

Each subgrid therefore has a 3D node and 3D GPU index. These indices are unique for each subgrid, and can be used to determine which subgrids need to communicate with which others. For example, the -x neighbor of subgrid might be [[1,1,0],[1,0,0]] is [[1,1,0],[0,0,0] (same node, -1 in x dimension of GPU index), where the first triplet is the X,Y,Z coordinate in the 3D node space, and the second is the coordinate in the 3D GPU space.

## 4.4 Subgrid Placement

After partitioning, the stencil library assigns each subgrid to a GPU. One node-level subgrid is assigned to each node. The stencil library does not attempt to evaluate node proximity, so node subgrids are assigned to nodes arbitrarily. This is because the OLCF summit system has a full-bandwidth fat-tree network, so the bandwidth between any pair of nodes is equal.

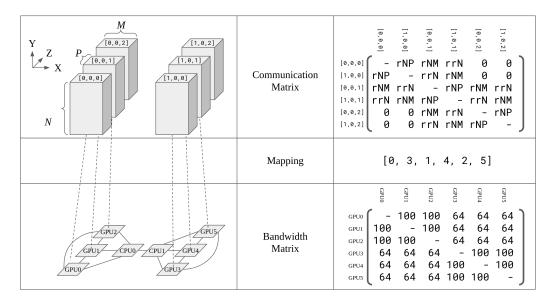

Figure 4.4: Example communication matrix (w in quadratic assignment problem) and bandwidth matrix (element-wise reciprocal of d). The result is the mapping (f), where the subgrid for row (or column) i of the communication matrix is mapped to GPU f(i). The entries in the communication matrix are given in terms of the subgrid size as well as the stencil radius r.

In contrast to the nodes within the system, the GPUs within a node do not have uniform bandwidth. Therefore, it may be desirable to place neighboring subgrids on GPUs that have fast interconnects between them. Within each node, this is modeled as a quadratic assignment problem (QAP). The quadratic assignment problem is concerned with assigning a set of P facilities to P locations, according to the *flow* between the facilities and the *distance* between the locations, with the goal of placing facilities with high flow close to one another. This is analogous to placing subgrids with high exchange volume on GPUs that have high communication bandwidth. The assignment is a bijection f between facilities and locations. Let real-valued square matrices w and d represent the flow between facilities i and j, and the distance between locations i and j, respectively. Then, the QAP minimizes the cost function

$$\sum_{i,j < P} w_{i,j} d_{f(i),f(j)}$$

the sum of the flow-distance products under f.

The flow matrix entries are the number of bytes of data exchanged between GPU subgrids, and the distance matrix entries are the element-wise reciprocal of a matrix B which captures the bandwidth of GPUs i and j in  $B_{i,j}$ . Figure 4.4 summarizes the construction of the matrices, and gives an example mapping. The CUDA driver provides the Nvidia Management Library libnvidia-ml, which can be used to infer the connection and bandwidth between GPUs in a system The quadratic assignment problem is NP-hard. In this work, we simply check all possible subdomain-GPU mappings on each node. Since the number of GPUs in a node is typically small, the cost of exhaustively searching all combinations is acceptable.

Figure 4.4 summarizes the scheme. On each OLCF Summit node, six subgrids are assigned. Their communication requirements (QAP flow) depend on their logical position within the grid. The QAP distance is determined by the GPU bandwidth. On Summit, each GPU triplet is connected by 2x NVLink2, for 100 GB/s bidirectional bandwidth. Any connection across the x-bus is limited to 64 GB/s. The element-wise inverse of the bandwidth is the distance, and the mapping is the bijection delivered by the QAP formulation.

## 4.5 Specialization

Once the compute region has been partitioned (Sec. 4.3) and assigned to GPUs according to the theoretical communication performance (Sec. 4.4),

Table 4.1: Summary of requirements for communication methods. " $\checkmark$ " means the communicating subregions must share the corresponding topology for the communication method to work. "Preference" refers to the heuristic preference for that communication method, if all requirements are met (1 is highest). "Async" refers to how the library implementation allows multiple communications to be overlapped.

| Same            |            |              |              |              |               |                |  |

|-----------------|------------|--------------|--------------|--------------|---------------|----------------|--|

| Method          | Preference | $\dots$ GPU  | rank         | node         | Async         | Notes          |  |

| Kernel          | 1          | $\checkmark$ | $\checkmark$ | $\checkmark$ | native        | peer access    |  |

| Memcpy          | 2          | ×            | $\checkmark$ | $\checkmark$ | native        | peer access    |  |

| ColocatedMemcpy | 3          | ×            | ×            | $\checkmark$ | state machine | peer access    |  |

| CudaAwareMPI    | 4          | ×            | ×            | ×            | native        | CUDA-Aware MPI |  |

| Staged          | 4          | ×            | ×            | ×            | state machine |                |  |

a fast communication method is selected based on the physical (node) and logical (rank) location of the two GPUs.

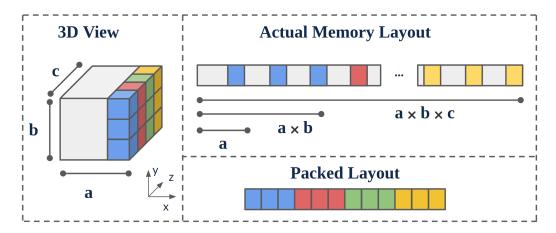

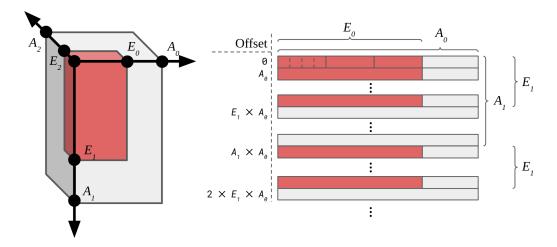

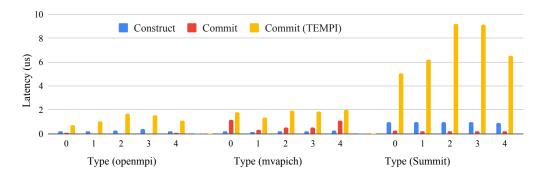

In general, the exchange operation consists of taking the (possibly) noncontiguous boundary gridpoints from the interior (non-ghost points) of the source subgrid, packing it into a contiguous buffer, sending that buffer to the destination GPU, and unpacking that buffer into the appropriate exterior of the destination subgrid. Figure 4.5 shows an example of a pack operation on a 3D region. In this example, we consider an XYZ storage order, yielding a non-contiguous storage for the 3D region shown. The result of the pack operation is to copy that data into a contiguous buffer.

In order to support high-performance exchanges in a variety of system configurations, the library implements five communication methods. The methods are selected appropriately for each sending and receiving pair of subgrids. All methods are asynchronous, allowing them to be freely overlapped, even within a single process. Table 4.1 shows the communication methods and when they apply.

#### 4.5.1 Baseline CUDA-aware MPI Communication

The baseline for the stencil library performance evaluation is a state-of-the art approach where every halo exchange uses a single CUDA-aware MPI\_-Isend/MPI\_Irecv with each other rank it needs to communicate with. This places the burden of overlapping and optimized communication on the MPI implementation instead of the application code.

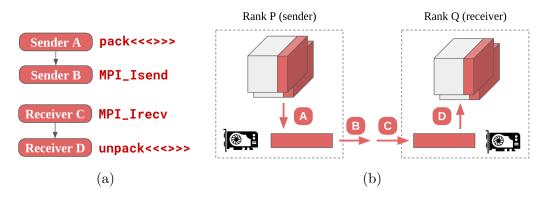

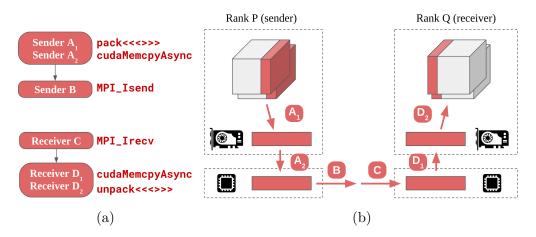

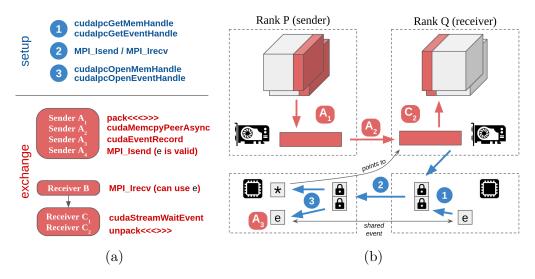

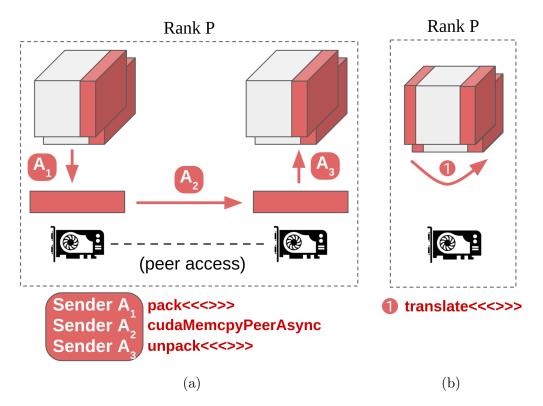

This "CUDA-aware" method shares the same general structure as all CUDA-

Figure 4.5: Example of packing for a 3D region. In general, the linear storage order of the subdomain in memory causes the elements of the 3D region to be strided. The pack operation places only those elements in a dense buffer with some predetermined order.

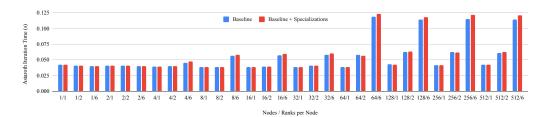

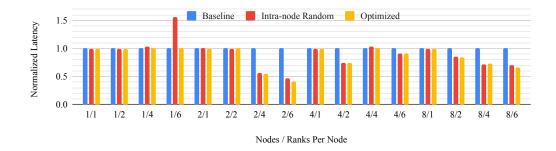

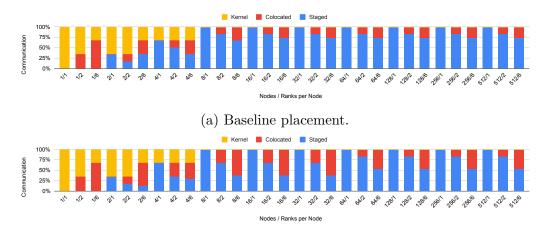

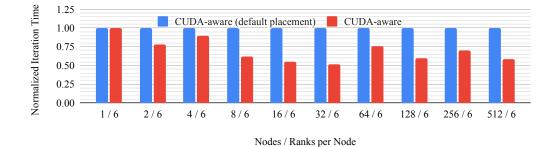

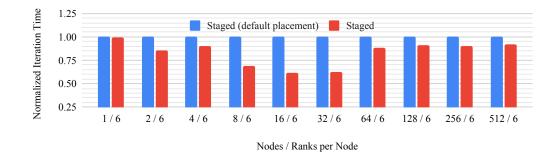

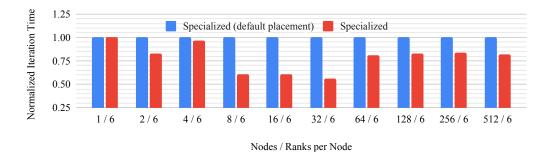

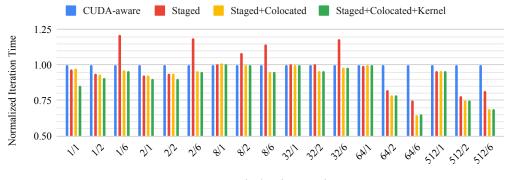

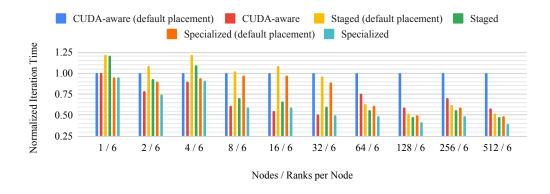

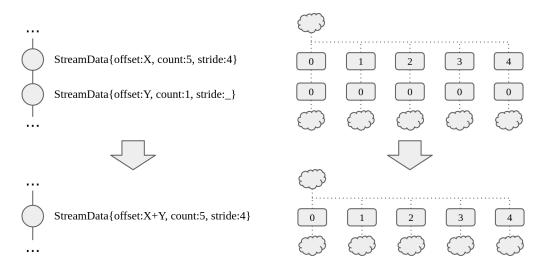

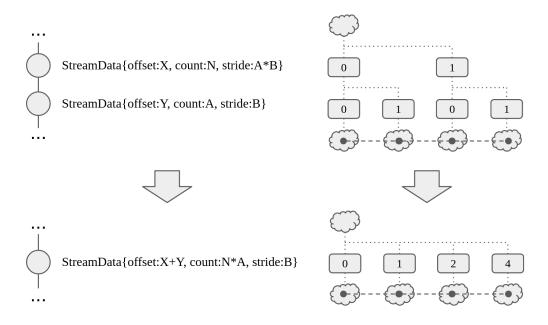

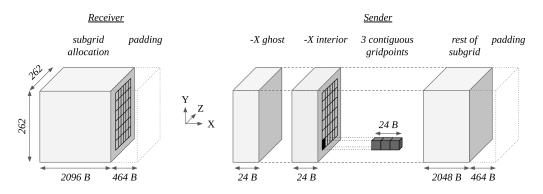

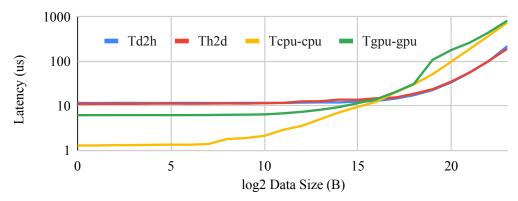

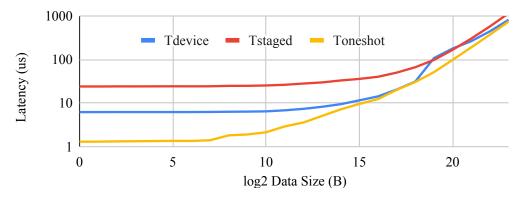

+MPI communicators in this work. Paired *sender* and *receiver* objects are created on the source and destination ranks to manage both ends of the communication. Therefore, a pair may handle the communication of more than one direction if the grid decomposition and boundary conditions cause a pair of ranks to be neighbors in multiple directions. This maximizes the size of the messages when the grid decomposition does not give each subgrid 26 unique neighbors, but also reduces the number of concurrent messages.